Testbänk för CPU top:

Varje enskilt block har konstruerats för att lösa så mycket som möjligt av operationerna internt, därmed kan dataflödet i längre signalvägar  mellan olika block hållas nere till fördel på flera sätt. Dels är testningen av varje enskilt block via testbänk lättare eftersom indata och enstaka styrsignaler genast resulterar i utdata på samma sätt som blocket skulle agera i den kompletta kunstruktionen. Om nödvändigt kan alla delblocken testas i en testbänk individuellt. Klarar alla delblocken testningen på detta sätt så måste även den kompletta kunstruktionen fungera. Det enda som då begränsar hastigheten för den totala funktionen är inbördes timing och tåligheten för eventuella störningar utifrån. Emellertid är denna testgång mycket tidsödande och ställer stora krav på konstruktionen av delblockens aktuella testbänk. Användningen av testbänkar för varje enskild komponent är ett alltför omfattande sätt att testa en större konstruktion.

mellan olika block hållas nere till fördel på flera sätt. Dels är testningen av varje enskilt block via testbänk lättare eftersom indata och enstaka styrsignaler genast resulterar i utdata på samma sätt som blocket skulle agera i den kompletta kunstruktionen. Om nödvändigt kan alla delblocken testas i en testbänk individuellt. Klarar alla delblocken testningen på detta sätt så måste även den kompletta kunstruktionen fungera. Det enda som då begränsar hastigheten för den totala funktionen är inbördes timing och tåligheten för eventuella störningar utifrån. Emellertid är denna testgång mycket tidsödande och ställer stora krav på konstruktionen av delblockens aktuella testbänk. Användningen av testbänkar för varje enskild komponent är ett alltför omfattande sätt att testa en större konstruktion.

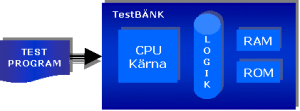

Efter instansieringen, dvs “ihopkopplingen” av processorn använde vi en mera tisdbesparande testmetod. En testbänk måste skrivas även för denna, men av mycket lägre kompexitet eftersom den endast skickar in data till konstrutionens översta nivå, dvs databussen, systemklockan och läs/skrivsignalerna. Testbänken i sig ska i vårt fall inte generera några interna signaler, utan möjliggör användningen av ett fristående testprogram, skrivet i assembler för att testa de olika operationerna. När assemblerprogrammet har kompilerats är koden av samma typ som de verkliga program processorn skall fungera under. Parallellt med processorns kärna finns både RAM och ROM som i testbänken sammanfogas med kontrollogiken. Kontrollogiken har till uppgift att koordinera användningen av systemets delade resurser som databuss och adressbuss tidsmässigt. Under körningen av testprogrammet tillåter CAD-programmets utvecklingsmiljö att man går in i konstruktionen oavsett nivå och avläser simuleringens utfall för varje instruktion. Man kan då tex undersöka varför inte den aktuella instruktionen exempelvis JZ exekveras. JZ är ett villkorligt hopp med given hoppadress och skall utföras om zero-flaggan är satt. Om inte hoppet utförs i simuleringen kan man se aktuell status för flaggregistret. Felet kan nu vara att zero-flaggan inte är satt trots resultatet noll. Inget hopp kan nu exekveras oavsett adress. Konstruktionen av det aktuella flaggregistret bör i det fallet undersökas närmare.