Registerbank

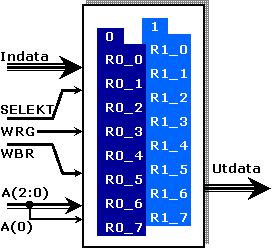

Processorns interna minne är en registerbank vilken består av två stycken banker som har till uppgift att lagra adresser och konstanter.

Bankerna benämns 0 och 1 och innehåller 8 stycken generella arbetsregister. Styrsignalen WBR väljer bank 0 för R0_0 –R0_7 eller bank 1 för R1_0 – R1_7. Signalen WRG bestämmer om den skall läsa från eller skriva till ett register. SELEKT är en styrsignal som vi har lagt till controllenheten, vilken pekar ut udda eller jämna register. De tre minst signifikanta bitarna av innehållet från instruktionsregistret tillsammans med styrsignalen SELEKT, sköter adressering av registren beroende på bank. SELEKT pekar alltid ut en jämn adress i registerbanken när processorn skall läsa från en minnesvariabel med hjälp av instruktionen LDAX eller om den skall skriva till en minnesvariabel med hjälp av instruktionen STAX.

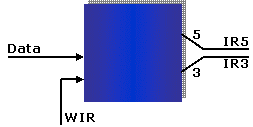

Instruktionsregister:

Instruktionsregistret i processorn är uppbyggt som ett synkront åtta bitars register med enable och asynkron reset. De högsta fem bitarna (b7-b3) avgör vilken instruktion processorn skall utföra, och de låga bitarna (b2-b0) specifierar instruktionen ytterligare med t ex hoppvillkor. Enklare instruktioner innefattar ej de lägre bitarna. Den första signalen kontrollblocket skickar ut efter uppstart eller efter reset är WIR, write instruction register. WIR tillsammans med systemklockan gör att processorn kan ta emot en instruktion från databussen.