Displaykontroll

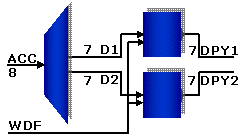

Blocket för displaykontroll är uppbyggt som en 8 bitars  binär, till 2 st 7 bitars hexadecimala avkodare tillsammans med två st 7-bitars register med enable och asynkron reset. Den binära ingången på 8 bitar delas upp så att den fungerar som drivare för två hexadecimala sjusegmentsdisplayer. De mest signifikanta bitarna[8 till 5] driver så display DPY1 och de minst signifikanta bitarna [4 till 0] driver display DPY2. De två registren uppdateras parallellt då WDP drivs hög från kontrollblocket.

binär, till 2 st 7 bitars hexadecimala avkodare tillsammans med två st 7-bitars register med enable och asynkron reset. Den binära ingången på 8 bitar delas upp så att den fungerar som drivare för två hexadecimala sjusegmentsdisplayer. De mest signifikanta bitarna[8 till 5] driver så display DPY1 och de minst signifikanta bitarna [4 till 0] driver display DPY2. De två registren uppdateras parallellt då WDP drivs hög från kontrollblocket.

Prototypkopplingen är gjord så att aktivt displayelement skall representeras av en låg signal, t.ex. A1 = “0000” genererar DPY1 = “1000000” vilket skriver ut tecknet 0 till displayen.

Insignaler Interna signaler Utsignaler

clk, reset A1, A2 = 4 bitar DPY1, DPY2 = 7 bitar

WDP = 1 bit D1, D2 = 7 bitar

ACC = 8 bitar