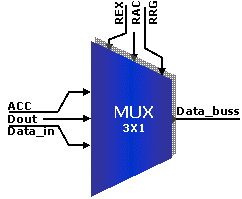

MUX:

Muxen 3×1 driver databussen från en av de tre 8 bitars ingångar från ackumulatorn, registerbanken eller dataingången. Kontrollblocket bestämmer med signalerna REX, RAC eller RRG vilken av ingångarna ska skickas ut på databussen.

| Ingångssignaler | Utgångssignal | ||

| RRG, RAC, REX | = 1 bit | DATA_BUSS = 8 bitar | = 8 bitar |

| ACC, DOUT, DATA_IN | = 8 bitar | ||

Med hjälp av muxen drivs databussen med data från ram/rom, data från register banken eller ackumulatorn.

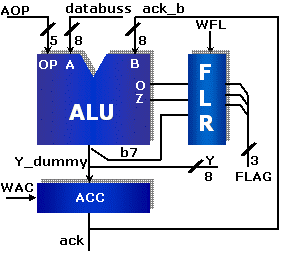

Aritmetisk Logisk Enhet, ALU

Den aritmetiska logiska enheten kan utföra ett antal operationer på dess inportar, och presentera resultatet på utporten. Den kan också generera tre statusflaggor för resultatanalys, även vid avbrottshantering sk interrupt. För att klara detta finns två parallella flagregister. Vid aritmetiska beräkningar betraktas samtliga talvärden i tvåkomplementform.

| Signalschema för ALU: | ||

| Y = A | Y = not A | Y = A and B |

| Y = A or B | Y = A + 1 | Y = A – 3 |

| Y = A + B | Y = A – B | |